La próxima ola de la Ley de Moore se basará en un concepto en desarrollo llamado cooptimización de la tecnología del sistema, dijo Ann B. Kelleher, gerente general de desarrollo tecnológico de Intel en una entrevista con Espectro IEEE antes de su charla plenaria en la Reunión de dispositivos de electrones (IEDM) de IEEE de 2022.

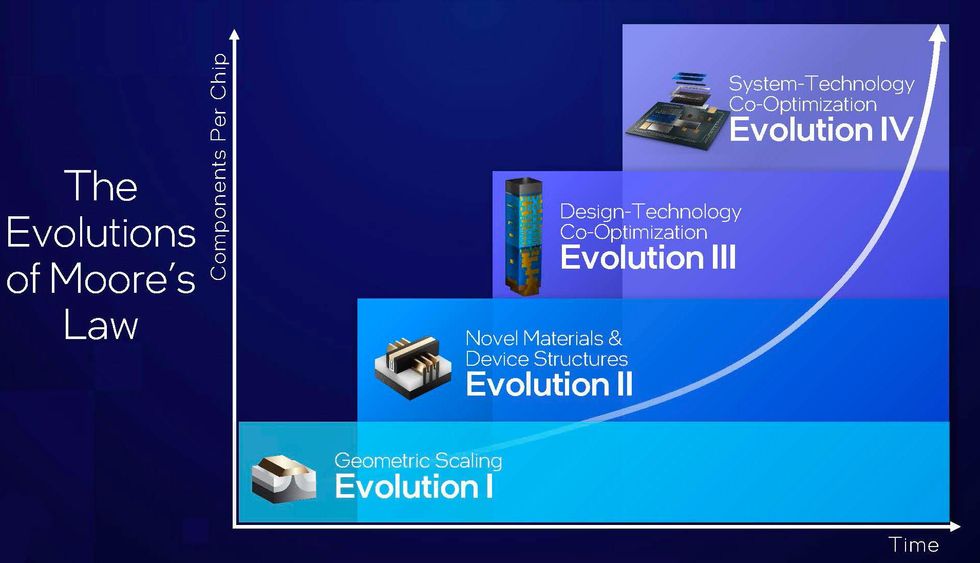

“La Ley de Moore se trata de aumentar la integración de funciones”, dice Kelleher. “Mientras miramos hacia los próximos 10 a 20 años, hay una tubería llena de innovación” que continuará la cadencia de productos mejorados cada dos años. Ese camino incluye las mejoras continuas habituales en los procesos y el diseño de semiconductores, pero la cooptimización de la tecnología del sistema (STCO) marcará la mayor diferencia.

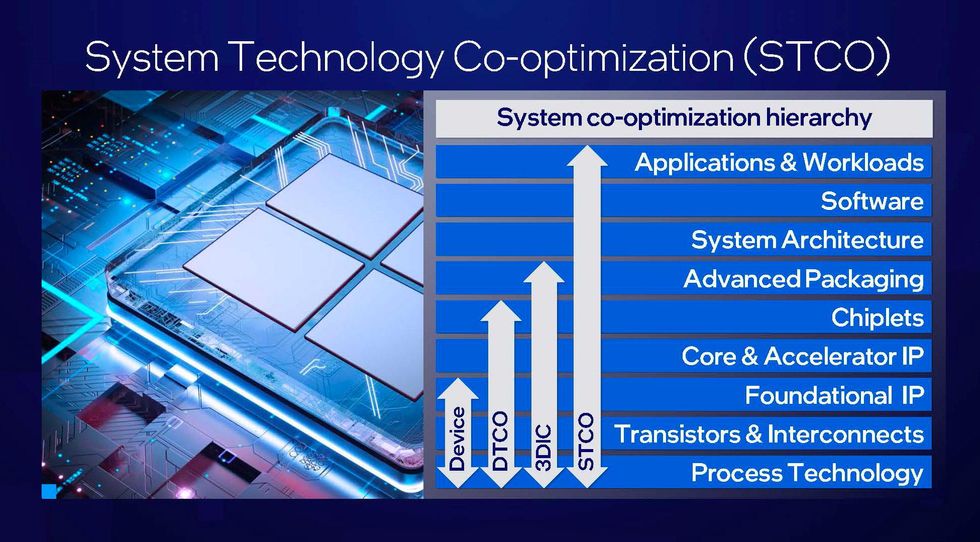

Kelleher lo llama una forma de desarrollo de “afuera hacia adentro”. Comienza con la carga de trabajo que un producto necesita soportar y su software, luego se reduce a la arquitectura del sistema, luego qué tipo de silicio debe estar dentro de un paquete y, finalmente, al proceso de fabricación de semiconductores. “Con la cooptimización de la tecnología del sistema, significa que todas las piezas se optimizan juntas para que obtenga la mejor respuesta para el producto final”, dice.

Ana B. KelleherIntel

STCO es una opción ahora en gran parte porque el empaque avanzado, como la integración 3D, permite la conexión de alto ancho de banda de chiplets (chips pequeños y funcionales) dentro de un solo paquete. Esto significa que lo que una vez serían funciones en un solo chip se puede desagregar en chipsets dedicados, cada uno de los cuales se puede fabricar utilizando la tecnología de proceso de semiconductores más óptima. Por ejemplo, Kelleher señala en su sesión plenaria que la informática de alto rendimiento exige una gran cantidad de memoria caché por núcleo de procesador, pero la capacidad de los fabricantes de chips para reducir la SRAM no avanza al mismo ritmo que la reducción de la lógica. Por lo tanto, tiene sentido construir cachés de SRAM y núcleos de cómputo como chipsets separados usando diferentes tecnologías de proceso y luego unirlos usando integración 3D.

Un ejemplo clave de STCO en acción, dice Kelleher, es el procesador Ponte Vecchio en el corazón de la supercomputadora Aurora. Está compuesto por 47 chiplets activos (así como 8 espacios en blanco para conducción térmica). Estos se unen mediante conexiones horizontales avanzadas (tecnología de empaquetado 2.5D) y apilamiento 3D. “Reúne silicio de diferentes fábricas y les permite unirse para que el sistema pueda funcionar frente a la carga de trabajo para la que está diseñado”, dice.

En IEDM, los ingenieros de Intel informarán que han aumentado diez veces la densidad de su tecnología de enlace híbrido 3D en comparación con lo que informaron en 2021. Una mayor densidad de conexión significa que se pueden desagregar más funciones de chip en chips separados, lo que a su vez brinda más potencial para usar STCO. para mejorar los resultados. Los pasos de enlace híbrido, es decir, la distancia entre las interconexiones, son de solo 3 micrómetros con esta nueva tecnología. Con eso, se puede separar aún más caché de los núcleos del procesador. Reducir el paso de enlace entre 2 micrómetros y 100 nanómetros podría significar poder comenzar a separar funciones lógicas que hoy deben estar en la misma pieza de silicio, según Kelleher.

El impulso para optimizar los sistemas mediante la desagregación de funciones está teniendo consecuencias para los futuros procesos de fabricación de semiconductores. La tecnología de proceso de semiconductores del futuro tiene que lidiar con las tensiones térmicas de un entorno empaquetado en 3D. Pero la tecnología de interconexión probablemente verá el mayor cambio. Kelleher dice que Intel está en camino de introducir una tecnología que llama PowerVia (entrega de energía trasera, en términos más generales) en 2024. PowerVia mueve la red de entrega de energía de un chip debajo del silicio, lo que reduce el tamaño de las celdas lógicas y reduce el consumo de energía. Pero también “nos brinda diferentes oportunidades en términos de lo que podemos y cómo podemos interconectarnos en el paquete”, dice Kelleher.

Kelleher enfatiza que STCO aún está en pañales. Las herramientas de automatización de diseño electrónico (EDA) ya han abordado el predecesor de STCO, la cooptimización de tecnología de diseño (DTCO), que se enfoca en optimizaciones a nivel de celda lógica y nivel de bloque funcional. “Pero algunos de los proveedores de herramientas EDA ya están trabajando en esto”, dice. “En el futuro, la atención se centrará en los métodos y herramientas que ayuden a habilitar STCO”.

A medida que se desarrolla STCO, es posible que los ingenieros de dispositivos tengan que desarrollarlo con él. “Por lo general, los ingenieros deberán continuar teniendo conocimiento sobre sus dispositivos, pero también deberán comenzar a comprender los casos de uso de su tecnología y sus dispositivos”, dice Kelleher. “Se requerirán más habilidades interdisciplinarias a medida que nos adentremos en un mundo STCO”.

Hoja de ruta de Intel

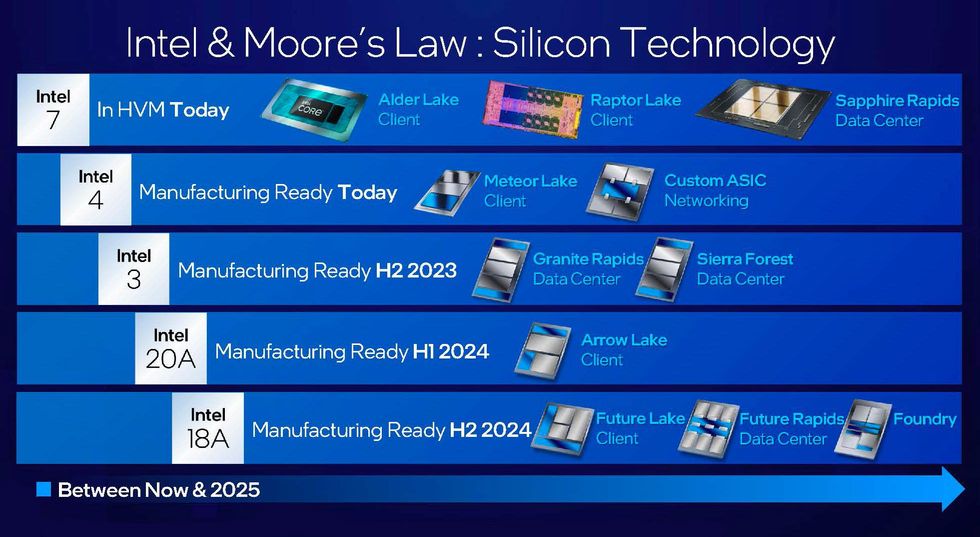

Kelleher también actualizó la hoja de ruta de Intel, vinculándola con la progresión de la Ley de Moore y la evolución del dispositivo desde la invención del primer transistor. La conclusión es que las cosas van por buen camino desde que Intel anunció su nueva hoja de ruta de fabricación hace menos de dos años, según Kelleher. Pero sí proporcionó algunos detalles sobre qué procesadores debutarían con la nueva tecnología.

Intel 20A, cuya introducción en fabricación está prevista para la primera mitad de 2024, sigue siendo el gran salto tecnológico. Simultáneamente, presenta una nueva arquitectura de transistores, RibbonFET (más generalmente llamados transistores de nanohojas o de compuerta completa), y la entrega de energía trasera PowerVia. Cuando se le preguntó sobre el riesgo involucrado, Kelleher explicó la estrategia.

“Ellos no tener hacerlo de una vez, pero vemos beneficios significativos al cambiar a PowerVia para habilitar el [RibbonFET] tecnología”, dice ella. El desarrollo está ocurriendo en paralelo para reducir el riesgo de retrasos, explica. Intel está ejecutando un proceso de prueba utilizando FinFET, la arquitectura de transistores que se usa hoy en día, con PowerVia. “Eso ha estado funcionando con mucho éxito y nos ha permitido acelerar nuestro trabajo de desarrollo”, dice.

El transistor del futuro

La charla de Kelleher se produce cuando la IEEE Electron Device Society celebra el 75.° aniversario de la invención del transistor. A Espectro IEEE, preguntamos a los expertos cómo podría ser el transistor en su cumpleaños número 100 en 2047. La opinión de Kelleher abarcó la larga vida útil de la tecnología de transistores, y señaló que el diseño del transistor planar duró desde 1960 hasta aproximadamente 2010, y que su sucesor, el FinFET, todavía está en funcionamiento. fuerte. “Ahora vamos al RibbonFET, que probablemente durará otros 20 años o más… así que espero que estemos en algún lugar con RibbonFET apilados”, sugirió. [Intel engineers describe that technology in the December 2022 issue of IEEE Spectrum.] Sin embargo, en ese momento, las cintas pueden estar hechas de semiconductores 2D en lugar de silicio.

De los artículos de su sitio

Artículos relacionados en la Web